# IMPLEMENTATION OF AREA EFFICIENT 8-BIT MULTIPLIER USING HIGHER ORDER COMPRESSORS

A Project report submitted in partial fulfilment of the requirements for the award of the degree of

## **BACHELOR OF TECHNOLOGY**

IN

## ELECTRONICS AND COMMUNICATION ENGINEERING

Submitted by

A. HARI SIVA GANESH (318126512003)

B. SANTHOSH KUMAR (318126512006)

B. BHANU PRAKASH (318126512007)

006) D. DURGA SANDEEP (318126512017)

Under the guidance of

Dr.K.V.G.Srinivas

**Assistant Professor**

## DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

ANIL NEERUKONDA INSTITUTE OF TECHNOLOGY AND SCIENCES

## (UGC AUTONOMOUS)

(Permanently Affiliated to AU, Approved by AICTE and Accredited by NBA & NAAC with 'A' Grade)

Sangivalasa, Bheemili mandal, Visakhapatnam dist.(A.P)

(2021-2022)

# DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING ANIL NEERUKONDA INSTITUTE OF TECHNOLOGY AND SCIENCES

(UGC AUTONOMOUS)

(Permanently Affiliated to AU, Approved by AICTE and Accredited by NBA & NAAC with 'A' Grade) Sangivalasa, Bheemili Mandal, Visakhapatnam dist.( A.P)

# CERTIFICATE

This is to certify that the project report entitled "IMPLEMENTATION OF 8-BIT AREA EFFICIENT MULTIPLIER USING HIGHER ORDER COMPRESSORS" submitted by A. Hari Siva Ganesh (318126512003), B. Santhosh Kumar (318126512006), B. Bhanu Prakash (318126512007), D. Durga Sandeep (318126512017) in partial fulfilment of the requirements for the award of the degree of Bachelor of Technology in Electronics & Communication Engineering of Andhra University, Visakhapatnam is a record of bonafide work carried out under my guidance and supervision.

Project Guide

Dr. K. V. G.Srinivas

Assistant Professor

Department of E.C.E

ANITS

Assistant Professor Department of E.C.E. Anil Neerukonda Institute of Technology & Sciences Sangivalasa, Visakhapatnam-531 162

Head of the Department

Dr. V. Rajalakshmi Professor & HOD Department of E.C.E ANITS

Fread of the Department Department of E C E Anil Neerukonda Institute of Technology & Sciences Sang ivalase=531,167

## ACKNOWLEDGEMENT

We would like to express our deep gratitude to our project guide **Dr.K.V.G.Srinivas** Assistant Professor, Department of Electronics and Communication Engineering, ANITS, for his guidance with unsurpassed knowledge and immense encouragement. We are grateful to **Dr. V. Rajyalakshmi**, Head of the Department, Electronics and Communication Engineering, for providing us with the required facilities for the completion of the project work.

We are very much thankful to the **Principal and Management**, **ANITS**, **Sangivalasa**, for their encouragement and cooperation to carry out this work.

We express our thanks to all **teaching faculty** of Department of ECE, whose suggestions during reviews helped us in accomplishment of our project. We would like to thank **all non-teaching staff** of the Department of ECE, ANITS for providing great assistance in accomplishment of our project.

We would like to thank our parents, friends, and classmates for their encouragement throughout our project period. At last but not the least, we thank everyone for supporting us directly or indirectly in completing this project successfully.

#### **PROJECT STUDENTS**

A. HARI SIVA GANESH (318126512003),

B. SANTHOSH KUMAR (318126512006),

B. BHANU PRAKASH (318126512007),

D. DURGA SANDEEP (318126512017).

#### ABSTRACT

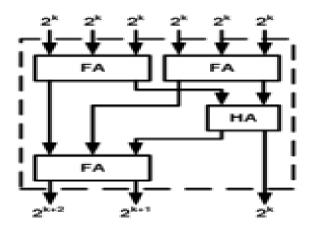

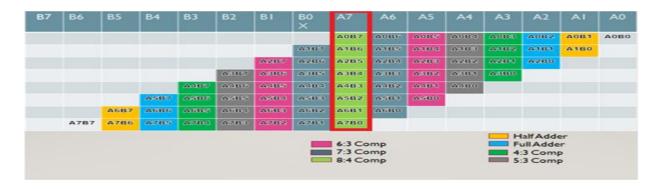

The accumulation of partial products is used to multiply binary bits. Full adders and half adders are commonly used for this. Various algorithms are utilized, including the Booth method, Ripple Carry, and Carry Save. The multiplier's performance in terms of latency, power, and area is determined by the number of stages used to sum the partial products. A higher order compressor-based area efficient 8x8 multiplier is proposed in this paper. To collect fragmentary products, we used the Wallace Tree structure. Carry save form is used in the structure. The carries generated in the adders are then passed on to the next stage, and so on, until the final stage. The final product is created using ripple carry form in the final stage. The Wallace Tree was chosen because it has a shorter critical path, resulting in reduced delay. Here we used two different methods to perform 8-bit multiplication and analysed both of them regarding area, power and some other parameters.

# CONTENTS

| ABSTRACT                                       |          |

|------------------------------------------------|----------|

| LIST OF FIGURES                                |          |

| LIST OF TABLES                                 |          |

| LIST OF ABBREVATIONS                           |          |

| CHAPTER 1 INTRODUCTION                         | 1        |

| 1.1 Project Objective                          | 1        |

| 1.2 Project Outline                            | 1        |

| CHAPTER 2 MULTIPLIERS                          | 2        |

| 2.1 Introduction to Multipliers                | 3        |

| 2.2 Types of Multipliers                       | 4        |

| CHAPTER 3 INTRODUCTION TO COMPRESSOR<br>ADDERS | 9        |

| 3.1 What are compressor adders                 | 9        |

| 3.2 Types of compressor adders                 | 9        |

| CHAPTER 4 OVERVIEW OF FPGA AND EDA             | 14       |

| SOFTWARE<br>4.1 Introduction                   | 14<br>14 |

| 4.2 Overview of digilent basys-3 board         | 14       |

| 4.2.1 Features of basys-3                      | 15       |

| 4.2.2 Power supply                             | 16       |

| 4.2.3 FPGA configuration                       | 18       |

| 4.2.4 Memory                                   | 22       |

| 4.2.5 Oscillators/Clocks                       | 22       |

| 4.2.6 USB-UART Bridge(serial port)             | 23       |

| 4.2.7 USB-HID Host                             | 23       |

| 4.2.8 VGA Port                                 | 28       |

| 4.2.9 Basic I/O                     | 32 |

|-------------------------------------|----|

| 4.2.10 Pmod Ports                   | 35 |

| 4.2.11 Built in Self-Test           | 38 |

| 4.3 Development flow                | 38 |

| 4.4 Overview of Verilog             | 40 |

| 4.5 Overview of EDA                 | 46 |

| <b>CHAPTER 5 SIMULATION RESULTS</b> | 59 |

| CONCLUSIONS                         | 66 |

| REFERENCES                          | 67 |

## LIST OF FIGURES

| Fig 2.1 Serial /parallel Multiplier                             | 3           |

|-----------------------------------------------------------------|-------------|

| Fig 2.2 Shift and add multiplier                                | 4           |

| Fig 2.3 Array multiplier                                        | 5           |

| Fig 2.4 Booth Multiplier                                        | 6           |

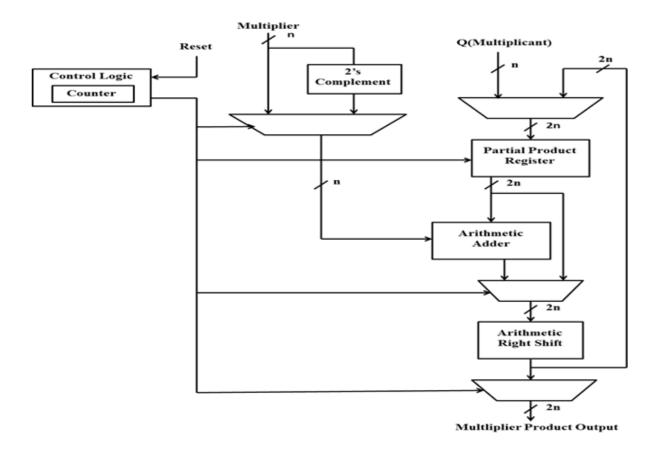

| Fig 2.5 Sequential multiplier                                   | 7           |

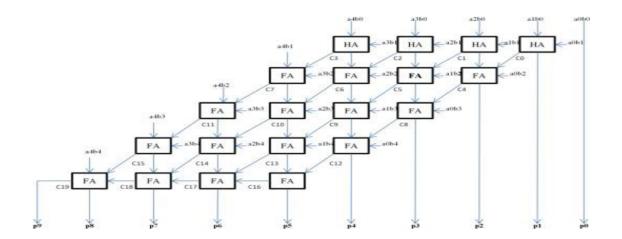

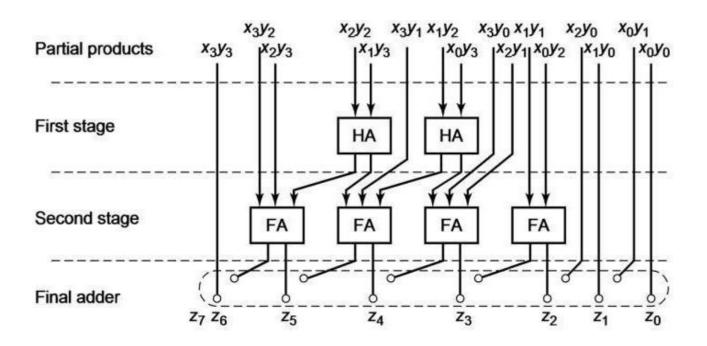

| Fig 2.6 Wallace tree multiplier                                 | 8           |

| Fig 3.2.1 circuit diagram of 4-2 compressor adder               | 10          |

| Fig 3.2.2 circuit diagram of 7-2 compressor adder               | 11          |

| Fig 3.2.3(a) circuit diagram of 5-3 compressor adder using gate | s <b>12</b> |

| Fig 3.2.3(b) modified circuit diagram of 5-3 compressor adder   | 12          |

| Fig 3.2.4 circuit diagram of 6-3 compressor adder               | 13          |

| Fig 3.2.5 circuit diagram of 7-3 compressor adder               | 13          |

| Fig 1 Basys-3 FPGA board with callouts                         | 16  |

|----------------------------------------------------------------|-----|

| Fig 2 Basys-3 Power circuit                                    | 17  |

| Fig 3 Basys-3 configuration options                            | 19  |

| Fig 4 Basys-3 external memory                                  | 22  |

| Fig 6 Basys-3 FT2232HQ connections                             | 23  |

| Fig 7 Basys-3 PK24 connections                                 | 24  |

| Fig 8 Ps/2 device to host timing diagram                       | 24  |

| Fig 9 Keyboard scan codes                                      | 25  |

| Fig 10 Mouse data format                                       | 27  |

| Fig 11 VGA Port                                                | 28  |

| Fig 12 Colour CRT display                                      | 29  |

| Fig 13 VGA Horizontal synchronization                          | 31  |

| Fig 14 Signal timings for a 640-pixel by 480 row display using | g a |

| 25 MHz pixel clock and 60 Hz vertical refresh                  | 32  |

| Fig 15 VGA display controller block diagram.                   | 32  |

| Fig 16 General purpose I/O devices on the Basys-3              | 33  |

| Fig 17 An un-illuminated seven-segment display and nine        |     |

| illumination patterns corresponding to decimal digits.         | 34  |

| Fig 18 Common anode circuit node                               | 34  |

| Fig 19 Four digit scanning display controller timing diagram   | 35  |

| Fig 20 Pmod ports; front view as loaded on PCB                 | 36  |

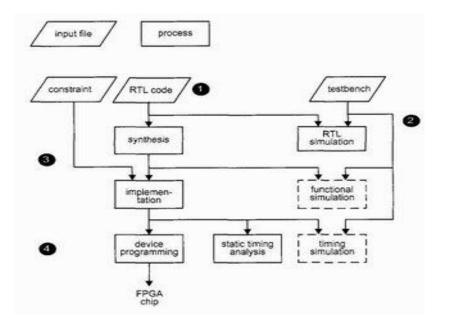

| Fig 21. Development flow                                       | 39  |

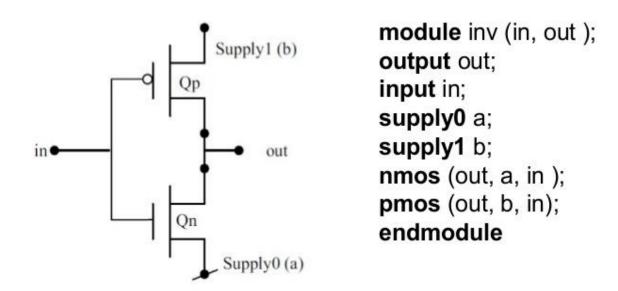

| Fig 22. CMOS inverter                                          | 43  |

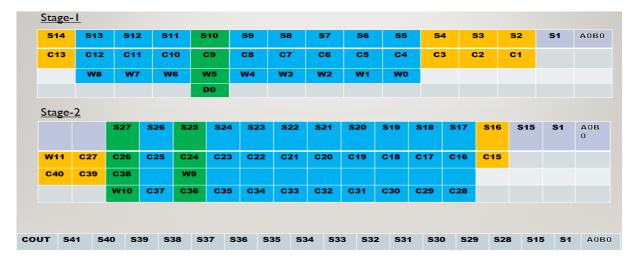

| Fig 23. RTL diagram                                            | 59  |

|                                                                |     |

| Fig 24. Synthesized schematic diagram | 60 |

|---------------------------------------|----|

| Fig 25. Design synthesize status      | 60 |

| Fig 26. LUT table                     | 60 |

| Fig 27. Logic and memory table        | 61 |

| Fig 28. Power report                  | 61 |

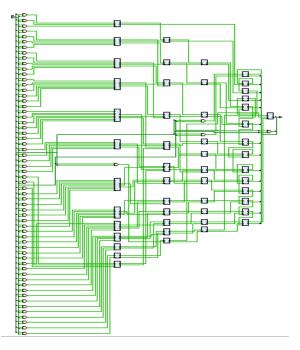

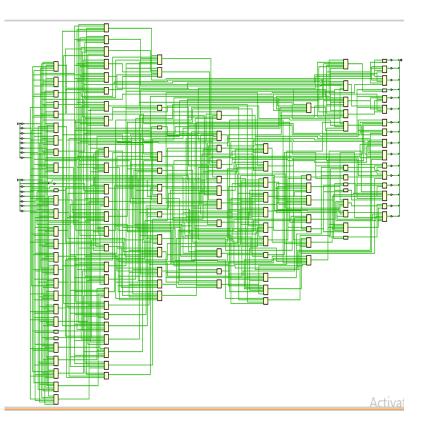

| Fig 29. RTL diagram                   | 62 |

| Fig 30. Synthesized schematic diagram | 62 |

| Fig 31. Design synthesize status      | 63 |

| Fig 32. LUT table                     | 63 |

| Fig 33. Power report                  | 63 |

| Fig 34. Simulation output results     | 64 |

|                                       |    |

## LIST OF TABLES

| Table 1. Basys3 components                            | 16        |

|-------------------------------------------------------|-----------|

| Table 2. Basys3 power supply                          | 18        |

| Table 3. Keyboard commands                            | 26        |

| Table 4. Microsoft Intellimouse-type extensions, comm | ands, and |

| actions.                                              | 27        |

| Table 5. Basys-3 Pmod pin assignment                  | 36        |

## LIST OF ABBREVATIONS

| DSP  | Digital Signal Processing                         |

|------|---------------------------------------------------|

| FPM  | Floating Point Multiplication                     |

| FPGA | Field Programmable Gate Array                     |

| HDL  | Hardware Description Language                     |

| LSB  | Least Significant Bit                             |

| IEEE | Institute of Electrical and Electronics Engineers |

| RCA  | Ripple Carry Adder                                |

| CLA  | Carry Look - Ahead Adder                          |

| CSA  | Carry Save Adder                                  |

| CA   | Carry-Select Adder                                |

| SPST | Spurious Power Suppression Technique              |

| DDR  | Double Data Rate                                  |

| LUT  | Look Up Tables                                    |

| PLL  | Phase-Locked Loop                                 |

| HR   | High Range                                        |

| ODT  | On-Die Terminations                               |

| РНҮ  | Physical Layer                                    |

| RTL  | Register Transfer Level                           |

| EDA  | Electronic Design Automation                      |

#### CHAPTER 1

#### **INTRODUCTION**

Multiplication is a fundamental function in arithmetic operations, and operations like multiply and Accumulate (MAC) and inner product are among the most commonly used Computation Intensive Arithmetic Functions (CIAF) in DSP applications like convolution, Fast Fourier Transform (FFT), filtering, and in microprocessors' arithmetic and logic units. Because multiplication takes up the majority of the execution time in most DSP algorithms, a high-speed multiplier is required. Multiplication time is still the most important component in determining a DSP chip's instruction cycle time. As the number of computer and signal processing applications grows, so does the demand for high-speed processing. In many real-time signal and image processing applications, higher throughput arithmetic operations are required to attain the desired performance. Multiplication is one of the most important mathematical operations in such applications, reducing the time delay and power consumption are critical criteria. Different multiplier architectures are presented in this paper.

#### **1.1 PROJECT OBJECTIVE:**

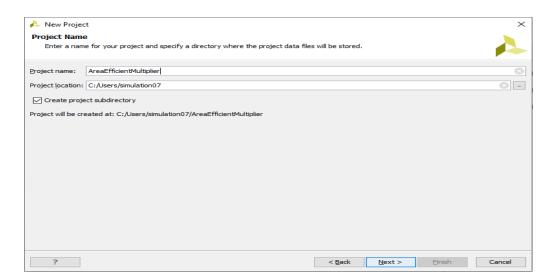

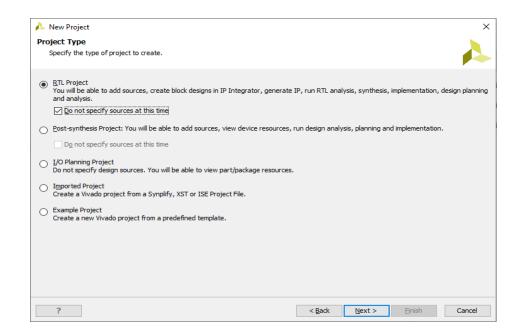

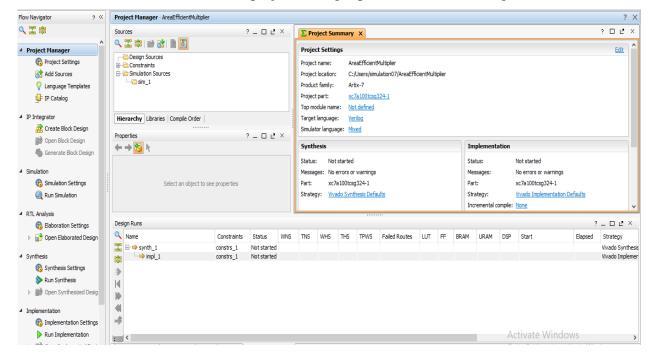

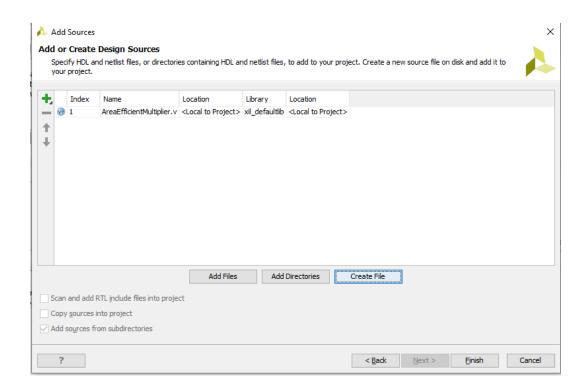

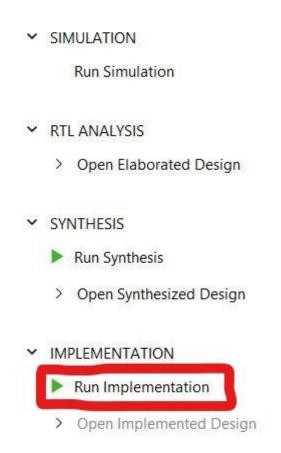

The main objective of this project is to design and implementation of area efficient multiplier with higher order compressors using Xilinx Vivado Software. The Synthesis and Implementation is done for different types of compressor adders using Xilinx Vivado. The performance is compared in terms of power, area and delay.

#### **1.2 PROJECT OUTLINE:**

- Project report is presented over the 6 remaining chapters.

- Chapter 2 Introduction to multipliers.

- Chapter 3 Introduction to compressor adders

- Chapter 4 Overview of fpga and eda software

- Chapter 5 Methodology

- Chapter 6 Results and conclusions

#### **CHAPTER 2**

## **INTRODUCTION TO MULTIPLIERS**

#### **2.1 MULTIPLIERS**

Multipliers play an important role in today's digital signal processing and various other applications. With advances in technology, many researchers have tried and are trying to design multipliers which offer either of the following design targets-high speed, low power consumption, regularity of layout and hence less area or even combination of them in one multiplier thus making them suitable for various high speed, low power and compact VLSI implementation.

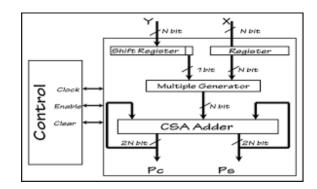

The common multiplication method is "add and shift" algorithm. In parallel multipliers number of partial products to be added is the main parameter that determines the performance of the multiplier. To reduce the number of partial products to be added, Modified Booth algorithm is one of themost popular algorithms.

To achieve speed improvements Wallace Tree algorithm can be used to reduce the number of sequential adding stages. Further by combining both Modified Booth algorithm and Wallace Tree technique we can seeadvantage of both algorithms in one multiplier.

However, with increasing parallelism, the number of shifts between the partial products and intermediate sums to be added will increase which may result in reduced speed, increase in silicon area due to irregularity of structure and also increased power consumption due to increase in interconnect resulting from complex routing.

On the other hand, "serial-parallel" multipliers compromise speed to achieve better performance for area and power consumption. The selection of a parallel or serial multiplier actually depends on the nature of application. In this lecture we introduce the multiplication algorithms and architecture and compare them in terms of speed, area, power and combination of these metrics.

#### 2.2 TYPES OF MULTIPLIERS

**Serial Multiplier:** Where area and power is of utmost importance and delay can be tolerated the serial multiplier is used. This circuit uses one adder to add the m \* n partial products.

**Serial/Parallel Multiplier:** One operand is fed to the circuit in parallel while the other is serial. N partial products are formed each cycle. On successive cycles, each cycle does the addition of one column of the multiplication table of M\*N PPs. The final results are stored in the output register after N+M cycles

Fig 2.1 Serial /parallel Multiplier

**Shift and Add Multiplier:** Depending on the value of multiplier LSB bit, a value of the multiplicand is added and accumulated. At each clock cycle the multiplier is shifted one bit to the right and its value is tested. If it is a 0, then only a shift operation is performed. If the value is a 1, then the multiplicand is added to the accumulator and is shifted by one bit to the right. After all the multiplier bits have been tested the product is in the accumulator. The accumulator is 2N (M+N) in size and initially the N, LSBs contains the Multiplier. The delay is N cycles maximum. This circuit has several advantages in asynchronous circuits

Fig 2.2 Shift and add multiplier

**Array Multipliers:** Array multiplier is well known due to its regular structure. Multiplier circuit is based on add and shift algorithm. Each partial product is generated by the multiplication of the multiplicand with one multiplier bit. The partial product are shifted according to their bit orders and then added. The addition can be performed with normal carrypropagate adder. N-1 adders are required where N is the multiplier length.

Fig 2.3 Array multiplier

**Booth Multipliers:** It is a powerful algorithm for signed-number multiplication, which treats both positive and negative numbers uniformly. For the standard add-shift operation, each multiplier bit generates one multiple of the multiplicand to be added to the partial product. If the multiplier is very large, then a large number of multiplicands have to be added. In this casethe delay of multiplier is determined mainly by the number of additions to be performed. If there is a way to reduce the number of the additions, the performance will get better. Booth algorithm is a method that will reduce the number of multiplicand multiplies. For a given rangeof numbers to be represented, a higher representation radix leads to fewer digits. Since a k-bitbinary number can be interpreted as K/2-digit radix-4 number, a K/3-digit radix-8 number, andso on, it can deal with more than one bit of the multiplier in each cycle by using high radix multiplication.

Fig 2.4 Booth Multiplier

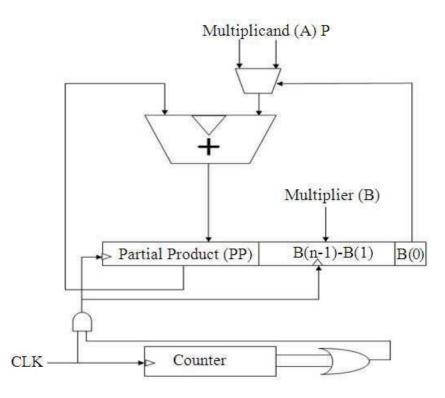

**Sequential multiplier:** If we want to multiply two binary number (multiplicand X has n bits and multiplier Y has m bits) using single n bit adder, we can build a sequential circuit that processes a single partial product at a time and then cycle the circuit m times. This type of circuit is called sequential multiplier. Sequential multipliers are attractive for their low area requirement. In a sequential multiplier, the multiplication process is divided into some sequential steps. In each step some partial products will be generated, added to an accumulated partial sum will be shifted to align the accumulated sum with partial product of next steps. Therefore, each step of a sequential multiplication consists of three different operations which are generating partial products, adding the generated partial products to the accumulated partial sum and shifting the partial sum.

Fig 2.5 Sequential multiplier

**Wallace tree Multiplier:** A Wallace tree is a efficient hardware implementation of a digital circuit that multiplies two integers. It was devised by the Australian computer scientist Chris Wallace in 1964.

The Wallace tree has three steps:

- Multiply (that is AND) each bit of one of the arguments, by each bit of the other, yielding n ^2 results. Depending on position of the multiplied bits, the wires carry different weights, for example wire of bit carrying result of is 128 (see explanation of weights below).

- 2. Reduce the number of partial products to two by layers of full and half adders.

- 3. Group the wires in two numbers, and add them with a conventional adder

The second step works as follows. As long as there are three or more wires with the same weight add a following layer: -

• Take any three wires with the same weights and input them into a Full adder. The result

will be an output wire of the same weight and an output wire with a higher weight for each three input wires.

- If there are two wires of the same weight left, input them into a Half adder

- If there is just one wire left, connect it to the next layer.

The benefit of the Wallace tree is that there are only reduction layers, and each layerhas O (1) propagation delay. As making the partial products is O (1) and the final addition is O (log n), the multiplication is only, not much slower than addition (however, much more expensive in the gate count). Naively adding partial products with regular adders would require O ( $\log^2 n$ ) time.

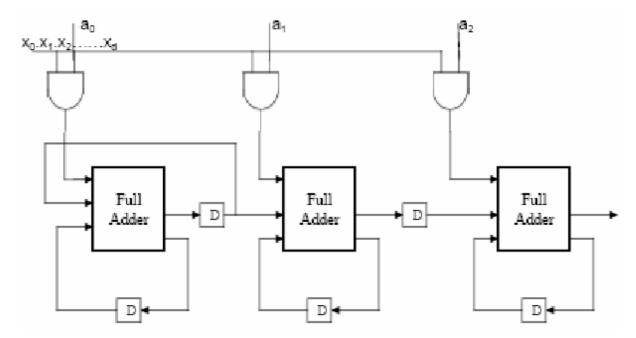

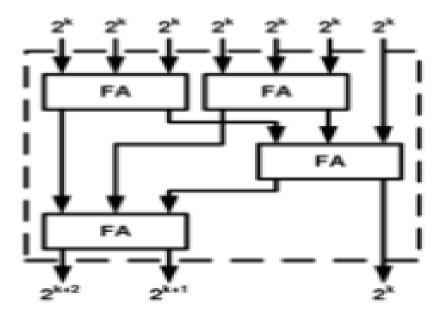

Fig 2.6 Wallace tree multiplier

# CHAPTER 3 INTRODUCTION TO COMPRESSOR ADDERS

## **3.1 COMPRESSOR ADDERS**

Compressor adders are basic circuits which add bits more than four at a time to give better delay results over the combinational circuits of half and full adders. The symbolic representation of compressor architecture is N - r where 'N' represents the number of the bits that are fed and 'r' represents the total count of the 1s present in N bits. It actually reduces the gate counts and delay in comparison to adder circuits and that is why named as compressor. A large part of research has been done in improving the circuits of lower compressors. Along with this, higher compressors are also implemented to add higher number of bits. The main compressor architectures which are used widely are 4-2,7-2, 5-3, 10-4, 15-4 and also 4-3,6-3,7-3,8-4.

## **3.2 TYPES OF COMPRESSOR ADDERS**

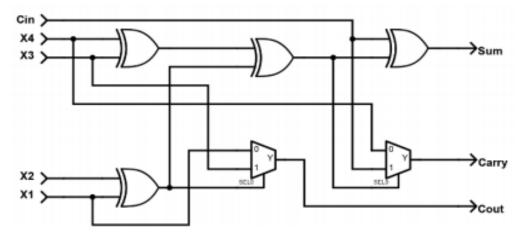

**4-2 COMPRESSOR ADDER:** A 4-2 compressor compresses four inputs plus one carry bit 'Cin' from the previous column into two outputs 'Sum' and 'Carry' plus one intermediate carry bit 'Cout' that is provided as Cin to the next column, as the name implies.

The 4-2 compressor's input and output relationship can be expressed mathematically as Cin+X4+X3+X2+X1 = Sum+2 (Carry+Cout). As shown in Fig., implementing a 4-2 compressor using basic cascading of full adders introduces a critical path delay of four XOR gates. As shown in Fig. 2, logical optimization reduces the critical path delay to three XOR gates, and this 4-2 compressor is considered a traditional model.

The traditional 4-2 compressor's Boolean equations are as follows: Sum = Cin X4 X3 X2 X1 Carry = (X4 X3 X2 X1) Cin + (X4 X3 X2 X1) X4 Cout = (X2 X1) X3 + (X2 X1) X1

Fig 3.2.1 circuit diagram of 4-2 compressor adder

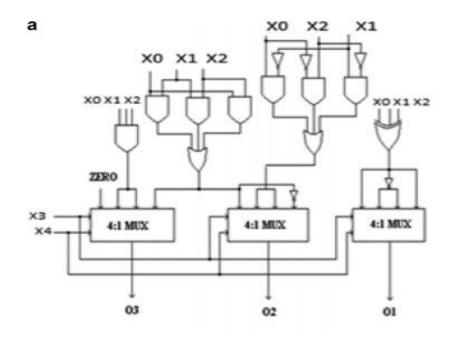

**5-3 COMPRESSOR ADDER:** A 5-3 compressor adder is a logical circuit in which maximum five bits can be added at the same time and three bits resultant of maximum value 101 is obtained. The circuit uses three 4:1 multiplexer. This multiplexer allows only one output to be high at a time and this property makes the multiplier fast and low power consuming circuit [13–15]. The circuit is reorganized in such a way that only 3 XOR operations are used instead of 5 XOR operations (in case of conventional 5-3 compressor) and other two inputs (X3 and X4) acts as a control signal. The conventional and the modified 5-3 compressor adder circuit are shown in

Fig 3.2.3(a) circuit diagram of 5-3 compressor adder using gates

Fig 3.2.3(b) modified circuit diagram of 5-3 compressor adder

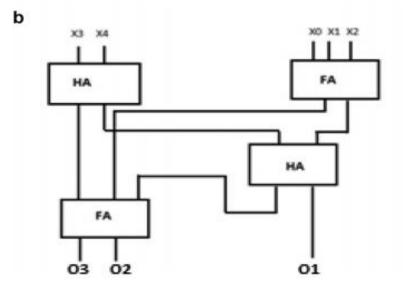

#### **6-3 COMPRESSOR ADDER:**

A combinational logic circuit of 6:3 compressor accepts six inputs and produces three outputs. The six input bits are summed up to produce the three bit output. In this three full adders and one half adder is used. The six input bits are given to two full adders which results in four outputs. These four output bits are fed to full adder and half adder as shown in the architecture and produces three outputs which are the final output bits of the result. The maximum output for a 6:3 compressor is 110.

Fig 3.2.4 circuit diagram of 6-3 compressor adder

#### 7-3 COMPRESSOR ADDER:

Combinational logic circuit of 7:3 compressor accepts seven inputs and produces three outputs. The seven input bits are summed up to produce the three bit cc output. In this, four full adders are used. The seven input bits are given to three full adders as shown in the figure. The first six bits are given to two full adders and the last bit is fed to another full adder. Finally the output bits are fetched as shown.

Fig 3.2.5 circuit diagram of 7-3 compressor adder

# CHAPTER 4 OVERVIEW OF FPGA AND EDA SOFTWARE

## **4.1 INTRODUCTION**

Developing a large FPGA –based system is an involved process that consists of many complex transformations and optimization algorithms. Software tools are needed to automate some of the tasks. We use Nexys4 Board which is a complete, ready-to- use digital circuit development platform based on the latest Artix-7 Field Programmable Gate Array (FPGA) (XC7A100T-ICSG324C) from Xilinx for synthesis and implementation, and use the Vivado Design Suite for simulation.

A Field Programmable Gate Array (FPGA) is a logic device that contains a two- dimensional add shift of generic logic cells and programmable switches. A logic cell can be programmed to perform a simple function, and a programmable switch can be customized to provide interconnection among the logic cells.

A custom design can be implemented by specifying the function of each logic cell and selectively setting the connection of each programmable switch. Once the design and synthesis are completed, we can use a simple adapter cable to download the desired logic cell and switch configuration to the FPGA device and obtain the custom circuit. Since this process can be done "in the field" rather than "in fabrication facility (fab)," the device is known as field programmable.

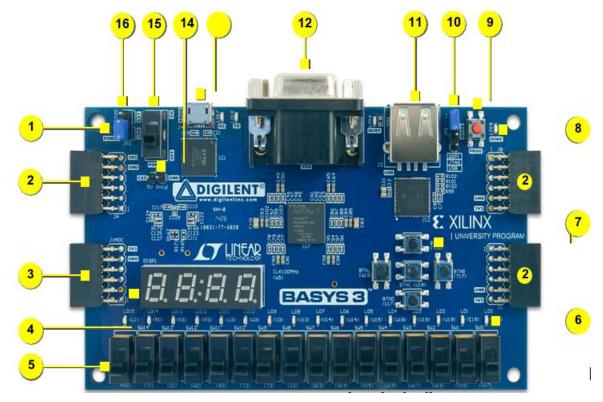

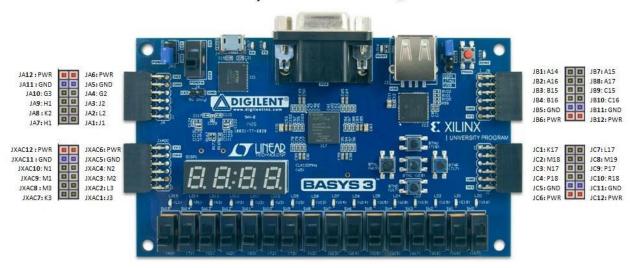

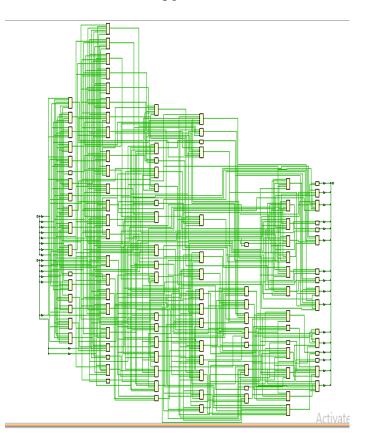

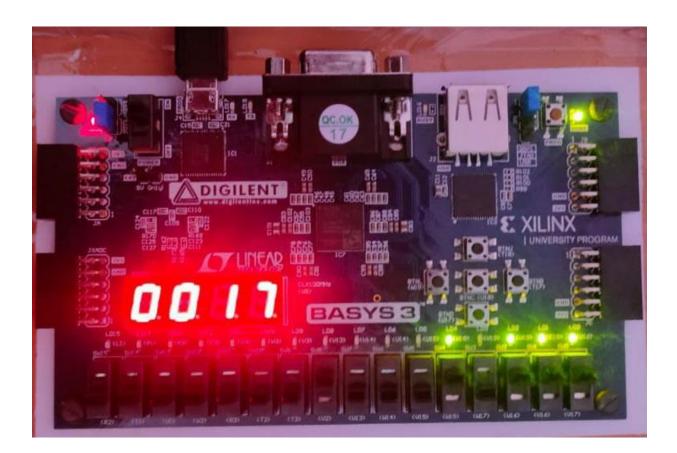

#### **4.2 OVERVIEW OF DIGILENT BASYS3 BOARD**

The Basys-3 board is a complete, ready-to-use digital circuit development platform based on the latest Artix-7 Field Programmable Gate Array (FPGA) from Xilinx®. With its high-capacity FPGA (Xilinx part number XC7A35T- 1CPG236C), low overall cost, and collection of USB, VGA, and other ports, the Basys-3 can host designs ranging from introductory combinational circuits to complex sequential circuits like embedded processors and controllers. It includes enough switches, LEDs, and other I/O devices to allow a large number of designs to be completed without the need for any additional hardware, and enough uncommitted FPGA I/O pins to allow designs to be expanded using Digilent Pmods or other custom boards and circuits.

# 4.2.1 Features of Basys-3

- 33,280 logic cells in 5200 slices (each slice contains four 6-input LUTs and 8 flip-flops)

- 1,800 Kbits of fast block RAM

- Five clock management tiles, each with a phase-locked loop(PLL)

- 90 DSP slices

- Internal clock speeds exceeding 450MHz

- On-chip analog-to-digital converter(XADC)

- 16 user switches

- 16 user LEDs

- 5 user push buttons

- 4-digit7-segmentdisplay

- Three Pmod ports

- Pmod for XADC signals

- 12-bit VGA output

- USB-UART Bridge

- Serial Flash

- Digilent USB-JTAG port for FPGA programming and communication

- USB HID Host for mice, keyboards and memory sticks

Fig1. Basys-3 FPGA board with callouts.

Table 1. Basys-3 components

| Callout | Component Description          | Callout | Component Description           |

|---------|--------------------------------|---------|---------------------------------|

| 1       | Power good LED                 | 9       | FPGA configuration reset button |

| 2       | Pmod port(s)                   | 10      | Programming mode jumper         |

| 3       | Analog signal Pmod port (XADC) | 11      | USB host connector              |

| 4       | Four digit 7-segment display   | 12      | VGA connector                   |

| 5       | Slide switches (16)            | 13      | Shared UART/ JTAG USB port      |

| 6       | LEDs (16)                      | 14      | External power connector        |

| 7       | Pushbuttons (5)                | 15      | Power Switch                    |

| 8       | FPGA programming done LED      | 16      | Power Select Jumper             |

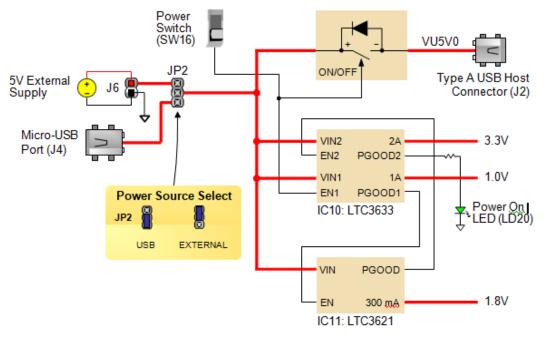

#### 4.2.2. Power Supplies

The Basys-3 board can receive power from the Digilent USB-JTAG port (J4) or from a 5V external power supply.Jumper JP3 (near the power switch) determines which source is used.

All Basys-3 power supplies can be turned on and off by a single logic-level power switch (SW16). A power-good LED(LD20), driven by the "power good" output of the LTC3633 supply, indicates that the supplies are turned on and operating normally. An overview of the Basys-3 power circuit is shown in Fig. 2.

Fig2. Basys-3 power circuit.

The USB port can deliver enough power for the vast majority of designs. A few demanding applications, including any that drive multiple peripheral boards, might require more power than the USB port can provide. Also, some applications may need to run without being connected to a PC's USB port. In these instances an external power supply or battery pack can be used.

An external power supply can be used by plugging into the external power header (J6) and setting jumper JP2 to "EXT". The supply must deliver 4.5VDC to 5.5VDC and at least 1A of current (i.e., at least 5W of power). Many suitable supplies can be purchased through Digi-Key or other catalog vendors.

An external battery pack can be used by connecting the battery's positive terminal to the "EXT" pin of J6 and the negative terminal to the "GND" pin of J6. The power provided to USB devices that are connected to Host connectorJ2 is not regulated. Therefore, it is necessary to limit the maximum voltage

of an external battery pack to 5.5V DC. The minimum voltage of the battery pack depends on the application; if the USB Host function (J2) is used, at least 4.6V needs to be provided. In other cases, the minimum voltage is 3.6V.

Voltage regulator circuits from Linear Technology create the required 3.3V, 1.8V, and 1.0V supplies from the mainpower input. Table 2 provides additional information (typical currents depend strongly on FPGA configuration and the values provided are typical of medium size/speed designs).

| Supply | Circuits                                        | Device        | Current (max/typical) |

|--------|-------------------------------------------------|---------------|-----------------------|

| 3.3V   | FPGA I/O, USB ports,<br>Clocks,<br>Flash, PMODs | IC10: LTC3633 | 2A/0.1 to 1.5A        |

| 1.0V   | FPGA Core                                       | IC10: LTC3633 | 2A/ 0.2 to 1.3A       |

| 1.8V   | FPGA Auxiliary and Ram                          | IC11: LTC3621 | 300mA/ 0.05 to 0.15A  |

Table 2. Basys-3 power supplies.

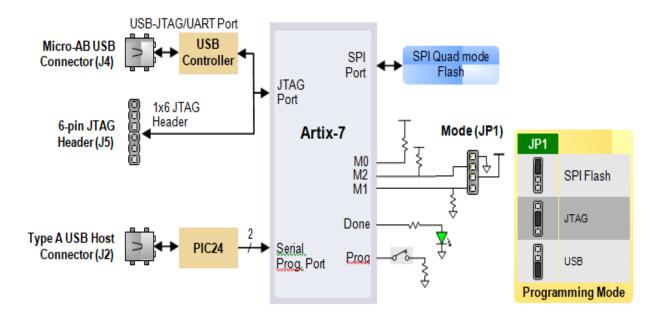

# 4.2.3 FPGA Configuration

After power-on, the Artix-7 FPGA must be configured (or programmed) before it can perform any functions. Youcan configure the FPGA in one of three ways:

A PC can use the Digilent USB-JTAG circuitry (portJ4, labeled "PROG") to program the FPGA any time thepower is on.

A file stored in the nonvolatile serial (SPI) flash device can be transferred to the FPGA using the SPI port.

A programming file can be transferred from a USB memory stick attached to the USB HID port.

Figure 3 shows the different options available for configuring the FPGA. An on-board "mode" jumper (JP1) selects between the programming modes.

Fig3. Basys-3 configuration options

The FPGA configuration data is stored in files called bit streams that have the .bit file extension. The Vivadosoftware from Xilinx can create bit streams from VHDL, Verilog®, or schematic-based source files.

Bit stream are stored in SRAM-based memory cells within the FPGA. This data defines the FPGA's logic functions and circuit connections, and it remains valid until it is erased by removing board power, by pressing the reset button attached to the PROG input, or by writing a new configuration file using the JTAG port.

An Artix-7 35T bit stream is typically 17,536,096 bits and can take a long time to transfer. The time it takes to program the Basys-3 can be decreased by compressing the bit stream before programming, and then allowing the FPGA to decompress the Bit stream itself during configuration. Depending on design complexity, compression ratios of 10x can be achieved. Bit stream compression can be enabled within the Xilinx Tools (Vivado) to occur during generation. For instructions on how to do this, consult the Xilinx documentation for the toolset being used.

After being successfully programmed, the FPGA will cause the "DONE" LED to illuminate. Pressing the "PROG" button at any time will reset the configuration memory in the FPGA. After being reset, the FPGA will immediately attempt to reprogram itself from whatever method has been selected by the programming mode jumper.

The following sections provide greater detail about programming the Basys-3 using the different methods available.

#### 4.2.3.1 JTAG Programming

The Xilinx Tools typically communicate with FPGAs using the Test Access Port and Boundary-Scan Architecture, commonly referred to as JTAG. During JTAG programming, a .bit file is transferred from the PC to the FPGA using the onboard Digilent USB-JTAG circuitry (port J4) or an external JTAG programmer, such as the Digilent JTAG-HS2 attached to port J5 (located below port JA). You can perform JTAG programming any time after the Basys-3 has been powered on regardless of what the mode jumper (JP1) is set to. If the FPGA is already configured, then the existing configuration is overwritten with the Bit stream being transmitted over JTAG. Setting the mode jumper to the JTAG setting (seen in Fig. 3) is useful to prevent the FPGA from being configured from any other Bit stream source until a JTAG programming occurs.

Programming the Basys-3 with an uncompressed Bit stream using the on-board USB\_JTAG circuitry usually takes around five seconds. JTAG programming can be done using the hardware server in Vivado. The demonstration project available at digilentinc.com provides an in-depth tutorial on how to program your board.

#### 4.2.3.2 JTAG Programming

When programming a nonvolatile flash device, a Bit stream file is transferred to the flash in a two-step process. First, the FPGA is programmed with a circuit that can program flash devices, and then data is transferred to the flash device via the FPGA circuit (this complexity is hidden from the user by the Xilinx Tools). After the flash device has been programmed, it can automatically configure the FPGA at a subsequent power-on or reset event as determined by the mode jumper setting (see Fig. 3). Programming files stored in the flash device will remain until they are overwritten, regardless of power-cycle events. Programming the flash can take as long as one or two minutes, which is mostly due to the lengthy erase process inherent to the memory technology. Once written, however, FPGA configuration can be very fast – less than a second. Bit stream compression, SPI bus width, and configuration rate are factors controlled by the Xilinx Tools that can affect configuration speed.

Quad-SPI programming can be performed using Vivado.

#### 4.2.3.3 USB Host Programming

You can program the FPGA from a pen drive attached to the USB-HID port (J2) by doing the following:

- 1. Format the storage device (Pen drive) with a FAT32 file system.

- 2. Place a single bit configuration file in the root directory of the storage device.

- 3. Attach the storage device to the Basys-3.

- 4. Set the JP1 Programming Mode jumper on the Basys-3 to "USB".

- 5. Push the PROG button or power-cycle the Basys-3.

The FPGA will automatically be configured with the .bit file on the selected storage device. Any .bit files that arenot built for the proper Artix-7 device will be rejected by the FPGA.

The Auxiliary Function Status, or "BUSY" LED (LD16), gives visual feedback on the state of the configuration process when the FPGA is not yet programmed:

- When steadily lit, the auxiliary microcontroller is either booting up or currently reading the configuration medium (pen drive) and downloading a Bit stream to the FPGA.

- A slow pulse means the microcontroller is waiting for a configuration medium to be plugged in.

- In case of an error during configuration, the LED will blink rapidly.

When the FPGA has been successfully configured, the behavior of the LED is application-specific. For example, if aUSB keyboard is plugged in, a rapid blink will signal the receipt of an HID input report from the keyboard.

## 4.2.4. Memory

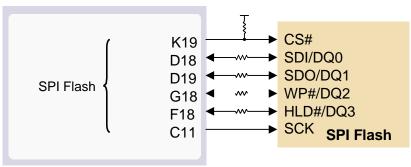

The Basys-3 board contains a 32Mbit non-volatile serial Flash device, which is attached to the Artix-7 FPGA using adedicated quad-mode (x4) SPI bus. The connections and pin assignments between the FPGA and the serial flash device are shown in Fig. 4.

FPGA configuration files can be written to the Quad SPI Flash (Spansion part number S25FL032), and mode settings are available to cause the FPGA to automatically read a configuration from this device at power on. An Artix-7 35T configuration file requires just over two Mbytes of memory, leaving approximately 48% of the flash device available for user data.

**NOTE**: Refer to the manufacturer's data sheets and the reference designs posted on Digilent's website for more information about the memory devices.

Fig4. Basys-3 external memory

# 4.2.5. Oscillators/Clocks

The Basys-3 board includes a single 100 MHz oscillator connected to pin W5 (W5 is a MRCC input on bank 34). Theinput clock can drive MMCMs or PLLs to generate clocks of various frequencies and with known phase relationships that may be needed throughout a design. Some rules restrict which MMCMs and PLLs may be driven by the 100 MHz input clock. For a full description of these rules and of the capabilities of the Artix-7 clocking resources, refer to the "7 Series FPGAs Clocking Resources User Guide" available from Xilinx.

Xilinx offers the LogiCORE<sup>TM</sup> Clocking Wizard IP to help users generate the different clocks required for a specific design. This wizard properly instantiates the needed MMCMs and PLLs based on the desired frequencies and phaserelationships specified by the user. The wizard will then output an easy to use wrapper component around these clocking resources that can be inserted into the user's design. The Clocking Wizard can be accessed from within IP Catalog, which can be found under the Project Manager section of the Flow Navigator in Vivado.

## 4.2.6. USB-UART Bridge (Serial Port)

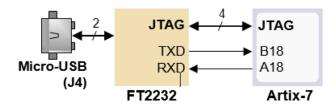

The Basys-3 includes an FTDI FT2232HQ USB-UART bridge (attached to connector J4) that allows you to use PC applications to communicate with the board using standard Windows COM port commands. Free USB-COM portdrivers, available from www.ftdichip.com under the "Virtual Com Port" or VCP heading, convert USB packets to UART/serial port data. Serial port data is exchanged with the FPGA using a two-wire serial port (TXD/RXD). After the drivers are installed, I/O commands can be used from the PC directed to the COM port to produce serial datatraffic on the B18 and A18 FPGA pins.

Two on-board status LEDs provide visual feedback on traffic flowing through the port: the transmit LED (LD18) and the receive LED (LD17). Signal names that imply direction are from the point-of-view of the DTE (Data Terminal Equipment), in this case the PC.

The FT2232HQ is also used as the controller for the Digilent USB-JTAG circuitry, but the USB-UART and USB-JTAG functions behave entirely independent of one another. Programmers interested in using the UART functionality of the FT2232 within their design do not need to worry about the JTAG circuitry interfering with the UART data transfers, and vice-versa. The combination of these two features into a single device allows the Basys-3 to be programmed, communicated with via UART, and powered from a computer attached with a single Micro USB cable. The connections between the FT2232HQ and the Artix-7 are shown in Fig. 6.

Fig6. Basys-3 FT2232HQ Connection

## 4.2.7.USB HID Host

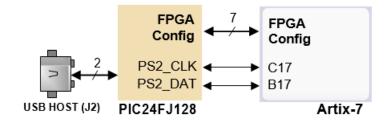

The Auxiliary Function microcontroller (Microchip PIC24FJ128) provides the Basys-3 with USB HID host capability. After power-up, the microcontroller is in configuration mode, either downloading a Bit stream to the FPGA or waiting for it to be programmed from other sources. Once the FPGA is programmed, the microcontroller switches to application mode, which in this case is USB HID Host mode. Firmware in the microcontroller can drive a mouse or a keyboard attached to the type A USB connector at J2 labeled "USB." Hub support is not currently available, soonly a single mouse or a single keyboard can be used. The PIC24 drives several signals into the FPGA – two are used to implement a

standard PS/2 interface for communication with a mouse or keyboard, and the others are connected to the FPGA's two-wire serial programming port, so the FPGA can be programmed from a file stored on a USB pen drive.

Fig7. Basys-3 PIC24 connections.

#### **4.2.7.1 HID CONTROLLER**

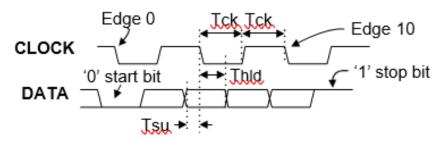

The Auxiliary Function microcontroller hides the USB HID protocol from the FPGA and emulates an old-style PS/2 bus. The microcontroller behaves just like a PS/2 keyboard or mouse would. This means new designs can re-use existing PS/2 IP cores. Mice and keyboards that use the PS/2 protocol use a two-wire serial bus (clock and data) to communicate with a host. On the Basys-3, the microcontroller emulates a PS/2 device while the FPGA plays the role of the host. Both the mouse and the keyboard use 11-bit words that include a start bit, data byte (LSB first), odd parity, and stop bit, but the data packets are organized differently, and the keyboard interface allows bi- directional data transfers (so the host device can illuminate state LEDs on the keyboard). Bus timings are shown in Fig. 8.

| Symbol           | Parameter                | Min  | Max  |

|------------------|--------------------------|------|------|

| Ι <sub>ck</sub>  | Clock time               | 30us | 50us |

| Ι <sub>su</sub>  | Data-to-clock setup time | 5us  | 25us |

| I <sub>HLD</sub> | Clock-to-data hold time  | 5us  | 25us |

Fig8. PS/2 device-to host timing diagram.

The clock and data signals are only driven when data transfers occur; otherwise they are held in the idle state at logic '1.' This requires that when the PS/2 signals are used in a design, internal pull-ups must be enabled in the FPGA on the data and clock pins. The clock signal is normally driven by the device, but may be held low by the hostin special cases. The timings define signal requirements for mouse-to-host communications and bi-directional keyboard communications. A PS/2 interface circuit can be implemented in the FPGA to create a keyboard or mouse interface.

When a keyboard or mouse is connected to the Basys-3, a "self-test passed" command (0xAA) is sent to the host. After this, commands may be issued to the device. Since both the keyboard and the mouse use the same PS/2 port, one can tell the type of device connected using the device ID. This ID can be read by issuing a Read ID command (0xF2). Also, a mouse sends its ID (0x00) right after the "self-test passed" command, which distinguishesit from a keyboard.

#### 4.2.7.2 Keyboard

The keyboard uses open-collector drivers so the keyboard, or an attached host device, can drive the two-wire bus (if the host device will not send data to the keyboard, then the host can use input-only ports).

PS/2-style keyboards use scan codes to communicate key press data. Each key is assigned a code that is sent whenever the key is pressed. If the key is held down, the scan code will be sent repeatedly about once every 100ms. When a key is released, an F0 key-up code is sent, followed by the scan code of the released key. If a key can be shifted to produce a new character (like a capital letter), then a shift character is sent in addition to the scan code and the host must determine which ASCII character to use. Some keys, called extended keys, send an E0 ahead of the scan code (and they may send more than one scan code). When an extended key is released, an E0 F0 key-up code is sent, followed by the scan code by the scan codes for most keys are shown in Fig. 9.

| ESC         F1         F2         F3         04           76         05         06         04         04         04                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | F4         F5         F6         F7         F8           0C         03         0B         83         0/                                                                                         |                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $ \begin{array}{c} \widehat{} \\ 0E \end{array} \begin{bmatrix} 1 \\ 16 \\ 1E \\ 1E \\ 1E \\ 26 \\ 25 \\ \hline \\ 25 \\ \hline \\ 25 \\ \hline \\ 25 \\ \hline \\ 10 \\ 15 \\ 1D \\ 10 \\ 24 \\ \hline \\ 24 \\ 24$ | $ \begin{bmatrix} 5 & % & 6 & \\ 2E & 36 & \\ 36 & 3D & 3E & 9 \\ 3E & 46 & \\ 46 & \\ R & T & Y & U & 1 \\ 2D & 2C & 35 & 3C & 43 \end{bmatrix} $                                              |                                                                                                                                                                                                                 |

| Caps Lock A S D 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $\begin{bmatrix} F \\ 2B \end{bmatrix} \begin{bmatrix} G \\ 34 \end{bmatrix} \begin{bmatrix} H \\ 33 \end{bmatrix} \begin{bmatrix} J \\ 3B \end{bmatrix} \begin{bmatrix} K \\ 42 \end{bmatrix}$ | $ \begin{array}{c} L \\ 4B \\ \end{array} \begin{array}{c} \vdots \\ 4C \\ \end{array} \begin{array}{c} \vdots \\ 52 \\ \end{array} \begin{array}{c} \text{Enter} \\ \leftarrow \\ 5A \end{array} \end{array} $ |

| Shift Z Z Z Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                 | $ \begin{vmatrix} 2 \\ -49 \end{vmatrix} \begin{vmatrix} 7 \\ 4A \end{vmatrix} \bigcirc \begin{vmatrix} 2 \\ -59 \end{vmatrix} $                                                                                |

| Ctrl Alt 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Space<br>29                                                                                                                                                                                     | Alt Ctrl E0 11 Ctrl                                                                                                                                                                                             |

#### Fig 9. Keyboard scan codes.

A host device can also send data to the keyboard. Table 3 shows a list of some common commands a host might send.

The keyboard can send data to the host only when both the data and clock lines are high (or idle). Because the host is the bus master, the keyboard must check to see whether the host is sending data before driving the bus. To facilitate this, the clock line is used as a "clear to send" signal. If the host drives the clock line low, the keyboard must not send any data until the clock is released. The keyboard sends data to the host in 11-bit words that contain a '0' start bit, followed by 8-bits of scan code (LSB first), followed by an odd parity bit, and terminated with a '1' stop bit. The keyboard generates 11 clock transitions (at 20 to 30 KHz) when the data is sent, and data is valid on the falling edge of the clock.

| Table 3. Keyboard comman | nds. |

|--------------------------|------|

|--------------------------|------|

| Command | Action                                                                                                                                                                                                                           |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ED      | Set Num Lock, Caps Lock, and Scroll Lock LEDs. Keyboard returns FA after receiving ED, then host sends a byte to set LED status: bit 0 sets Scroll Lock, bit 1 sets Num Lock, and bit 2 sets Caps lock. Bits 3 to 7 are ignored. |

| EE      | Echo (test). Keyboard returns EE after receiving EE.                                                                                                                                                                             |

| F3      | Set scan code repeat rate. Keyboard returns F3 on receiving FA, then host sends second byte to set the repeat rate.                                                                                                              |

| FE      | Resend. FE directs keyboard to re-send most recent scan code.                                                                                                                                                                    |

| FF      | Reset. Resets the keyboard.                                                                                                                                                                                                      |

## 4.2.7.3 MOUSE

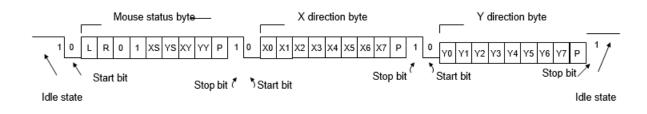

Once entered in stream mode and data reporting has been enabled, the mouse outputs a clock and data signal when it is moved. Otherwise, these signals remain at logic '1.' Each time the mouse is moved, three 11-bit words are sent from the mouse to the host device, as shown in Fig. 10. Each of the 11-bit words contains a '0' start bit, followed by 8 bits of data (LSB first), followed by an odd parity bit, and terminated with a '1' stop bit. Thus, each data transmission contains 33 bits, where bits 0, 11, and 22 are '0' start bits, and bits 11, 21, and 33 are '1' stop bits. The three 8-bit data fields contain movement data as shown in the Fig. 10. Data is valid at the falling edge of the clock, and the clock period is 20 to 30 KHz.

The mouse assumes a relative coordinate system wherein moving the mouse to the right generates a positive number in the X field, and moving to the left generates a negative number. Likewise, moving the mouse up generates a positive number in the Y field, and moving down represents a negative

number (the XS and YS bits in the status byte are the sign bits – a '1' indicates a negative number). The magnitude of the X and Y numbers represent the rate of mouse movement; the larger the number, the faster the mouse is moving (the XV and YV bits in the status byte are movement overflow indicators – a '1' means overflow has occurred). If the mouse moves continuously, the 33-bit transmissions are repeated every 50ms or so. The L and R fields in the status byte indicate Left and Right button presses (a '1' indicates that the button is being pressed).

Fig 10. Mouse data format.

The microcontroller also supports Microsoft® IntelliMouse®-type extensions for reporting back a third axis representing the mouse wheel, as shown in Table 4.

| Command | Action                                                                                                                                                                                                                                                                 |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EA      | Set stream mode. The mouse responds with "acknowledge" (0xFA) then resets its movement counters and enters stream mode.                                                                                                                                                |

| F4      | Enable data reporting. The mouse responds with "acknowledge" (0xFA) then<br>enables data<br>reporting and resets its movement counters. This command only affects<br>behavior in streammode. Once issued, mouse movement will automatically<br>generate a data packet. |

| F5      | Disable data reporting. The mouse responds with "acknowledge" (0xFA) then disables data reporting and resets its movement counters.                                                                                                                                    |

| F3      | Set mouse sample rate. The mouse responds with "acknowledge" (0xFA) then reads one morebyte from the host. This byte is then saved as the new sample rate, and a new "acknowledge" packet is issued.                                                                   |

| FE      | Resend. FE directs mouse to re-send last packet.                                                                                                                                                                                                                       |

| FF      | Reset. The mouse responds with "acknowledge" (0xFA) then enters reset mode.                                                                                                                                                                                            |

Table 4. Microsoft Intelli mouse-type extensions, commands, and actions.

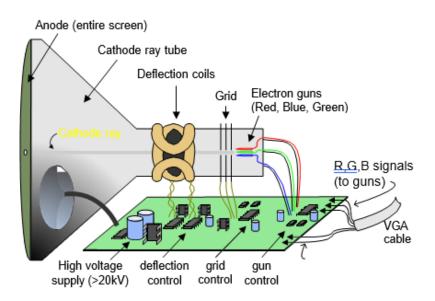

#### 4.2.8 VGA PORT

**NOTE:** A helpful way to understand the way that VGA signals are transmitted is to understand the method of whichCRT (Cathode Ray Tubes) function for displaying images. Although the technology may seem outdated, it is from this legacy that many of the signal names and timings have originated.

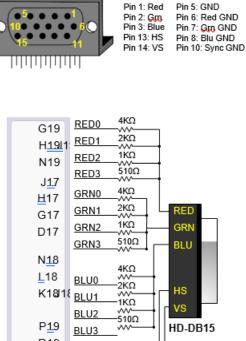

The Basys-3 board uses 14 FPGA signals to create a VGA port with 4-bits per colour and the two standard sync signals (HS – Horizontal Sync, and VS – Vertical Sync). The colour signals use resistordivider circuits that work in conjunction with the 75 ohm termination resistance of the VGA display to create 16 signal levels each on the red, green, and blue VGA signals. This circuit, shown in Fig. 11, produces video colour signals that proceed in equal increments between 0V (fully off) and 0.7V (fully on). Using this circuit, 4096 different colours can be displayed, one for each unique 12-bit pattern. A video controller circuit must be created in the FPGA to drive the sync and colour signals with the correct timing in order to produce a working display system.

Artix-7

Fig 11.VGA port

#### 4.2.8.1 VGA SYSTEM TIMING

VGA signal timings are specified, published, copyrighted, and sold by the VESA® organization (<u>www.vesa.org</u>). Thefollowing VGA system timing information is provided as an example of how a VGA monitor might be driven in 640by 480 mode.

NOTE: For more precise information, or for information on other VGA frequencies, refer to documentation available at the VESA website.

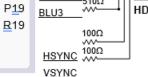

CRT-based VGA displays use amplitude-modulated moving electron beams (or cathode rays) to display information on a phosphor-coated screen. LCD displays use an array of switches that can impose a voltage across a small amount of liquid crystal, thereby changing light permittivity through the crystal on a pixel-by-pixel basis. Although the following description is limited to CRT displays, LCD displays have evolved to use the same signal timings as CRT displays (so the "signals" discussion below pertains to both CRTs and LCDs). Color CRT displays use three electron beams (one for red, one for blue, and one for green) to energize the phosphor that coats the inner side of the display end of a cathode ray tube (see Fig. 12).

Fig 12. Colour CRT display.

Electron beams emanate from "electron guns" which are finely-pointed heated cathodes placed in close proximity to a positively charged annular plate called a "grid." The electrostatic force imposed by the grid pulls rays of energized electrons from the cathodes, and those rays are fed by the current that flows into the cathodes. These particle rays are initially accelerated towards the grid, but they soon fall under the influence of the much larger electrostatic force that results from the entire

phosphor-coated display surface of the CRT being charged to 20kV (or more). The rays are focused to a fine beam as they pass through the center of the grids, and then they accelerate to impact on the phosphor-coated display surface. The phosphor surface glows brightly at the impact point, and it continues to glow for several hundred microseconds after the beam is removed. The larger the current fed into the cathode, the brighter the phosphor will glow.

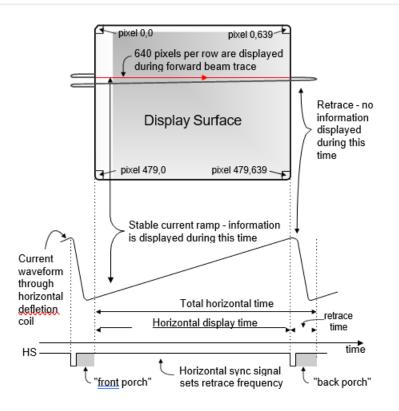

Between the grid and the display surface, the beam passes through the neck of the CRT where two coils of wire produce orthogonal electromagnetic fields. Because cathode rays are composed of charged particles (electrons), they can be deflected by these magnetic fields. Current waveforms are passed through the coils to produce magnetic fields that interact with the cathode rays and cause them to transverse the display surface in a "raster" pattern, horizontally from left to right and vertically from top to bottom, as shown in Fig. 13. As the cathode ray moves over the surface of the display, the current sent to the electron guns can be increased or decreased to change the brightness of the display at the cathode ray impact point.

Information is only displayed when the beam is moving in the "forward" direction (left to right and top to bottom), and not during the time the beam is reset back to the left or top edge of the display. Much of the potential displaytime is therefore lost in "blanking" periods when the beam is reset and stabilized to begin a new horizontal or vertical display pass. The size of the beams, the frequency at which the beam can be traced across the display, and the frequency at which the electron beam can be modulated determine the display resolution.

Modern VGA displays can accommodate different resolutions, and a VGA controller circuit dictates the resolution by producing timing signals to control the raster patterns. The controller must produce synchronizing pulses at 3.3V (or 5V) to set the frequency at which current flows through the deflection coils, and it must ensure that videodata is applied to the electron guns at the correct time. Raster video displays define a number of "rows" that corresponds to the number of horizontal passes the cathode makes over the display area, and a number of "columns" that corresponds to an area on each row that is assigned to one "picture element" or pixel. Typical displays use from 240 to 1200 rows and from 320 to 1600 columns. The overall size of a display and the number of rows and columns determines the size of each pixel.

Fig 13. VGA horizontal synchronization.

Video data typically comes from a video refresh memory; with one or more bytes assigned to each pixel location (the Basys-3 uses 12-bits per pixel). The controller must index into video memory as the beams move across the display, and retrieve and apply video data to the display at precisely the time the electron beam is moving across agiven pixel.

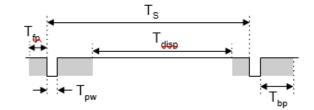

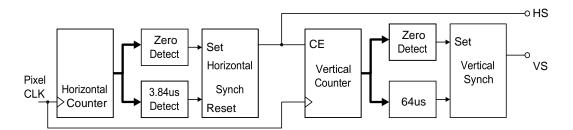

A VGA controller circuit must generate the HS and VS timings signals and coordinate the delivery of video data based on the pixel clock. The pixel clock defines the time available to display one pixel of information. The VS signal defines the "refresh" frequency of the display, or the frequency at which all information on the display is redrawn. The minimum refresh frequency is a function of the display's phosphor and electron beam intensity, with practical refresh frequencies falling in the 50Hz to 120Hz range. The number of lines to be displayed at a given refresh frequency defines the horizontal "retrace" frequency. For a 640-pixel by 480-row display using a 25 MHz pixel clock and 60 +/-1Hz refresh, the signal timings shown in Fig. 14 can be derived. Timings for sync pulse width and front and back porch intervals (porch intervals are the pre- and post-sync pulse times during which information cannot be displayed) are based on observations taken from actual VGA displays.

| Symbol          | Parameter    | Ve      | rtical Sy | nc    | Horiz.  | Sync              |

|-----------------|--------------|---------|-----------|-------|---------|-------------------|

| Symbol          | Farameter    | Time    | Clocks    | Lines | Time    | <mark>Çiks</mark> |

| т <sub>s</sub>  | Sync pulse   | 16.7ms  | 416,800   | 521   | 32 us   | 800               |

| T disp          | Display time | 15.36ms | 384,000   | 480   | 25.6 us | 640               |

| Tpw             | Pulse width  | 64 us   | 1,600     | 2     | 3.84 us | 96                |

| ⊤f₽             | Front porch  | 320 us  | 8,000     | 10    | 640 ns  | 16                |

| т <sub>ьр</sub> | Back porch   | 928 us  | 23,200    | 29    | 1.92 us | 48                |

**Fig 14**. Signal timings for a 640-pixel by 480 row display using a 25 MHz pixel clock and 60 Hz vertical refresh.

A VGA controller circuit, such as the one diagramed in Fig. 15, decodes the output of a horizontalsync counter driven by the pixel clock to generate HS signal timings. You can use this counter to locate any pixel location on a given row. Likewise, the output of a vertical-sync counter that increments with each HS pulse can be used to generate VS signal timings, and you can use this counter to locate any given row. These two continually running counters can be used to form an address into video RAM. No time relationship between the onset of the HS pulseand the onset of the VS pulse is specified, so you can arrange the counters to easily form video RAM addresses, or to minimize decoding logic for sync pulse generation.

Fig 15. VGA display controller block diagram.

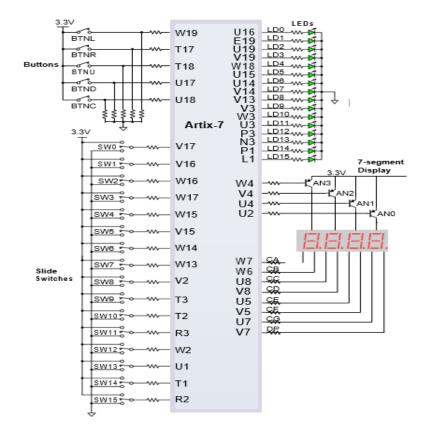

## 4.2.9. BASIC I/O

The Basys-3 board includes sixteen slide switches, five push buttons, sixteen individual LEDs, and a four-digit seven- segment display, as shown in Fig.16. The pushbuttons and slide switches are connected to the FPGA via series resistors to prevent damage from inadvertent short circuits (a short circuit could occur if an FPGA pin assigned to a pushbutton or slide switch was inadvertently defined

as an output). The five pushbuttons, arranged in a plus-sign configuration, are "momentary" switches that normally generate a low output when they are at rest, and a high output only when they are pressed. Slide switches generate constant high or low inputs depending on their position.

Fig 16. General purpose I/O devices on the Basys-3.

The sixteen individual high-efficiency LEDs are anode-connected to the FPGA via 330 ohm resistors, so they will turn on when a logic high voltage is applied to their respective I/O pin. Additional LEDs, which are not user- accessible, indicate power-on, FPGA programming status, and USB port status.

## 4.2.9.1 Seven-Segment Display

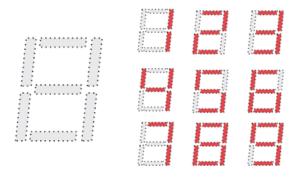

The Basys-3 board contains one four-digit common anode seven-segment LED display. Each of the four digits is composed of seven segments arranged in a "figure 8" pattern, with an LED embedded in each segment. Segment LEDs can be individually illuminated, so any one of 128 patterns can be displayed on a digit by illuminating certainLED segments and leaving the others dark, as shown in Fig. 17. Of these 128 possible patterns, the ten corresponding to the decimal digits are the most useful.

Fig 17. An un-illuminated seven-segment display and nine illumination patterns corresponding to decimal digits.

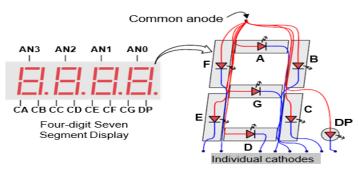

The anodes of the seven LEDs forming each digit are tied together into one "common anode" circuit node, but the LED cathodes remain separate, as shown in Fig. 18. The common anode signals are available as four "digit enable" input signals to the 4-digit display. The cathodes of similar segments on all four displays are connected into seven circuit nodes labeled CA through CG (for example, the four "D" cathodes from the four digits are grouped together into a single circuit node called "CD"). These seven cathode signals are available as inputs to the 4-digit display.

This signal connection scheme creates a multiplexed display, where the cathode signals are common to all digits but they can only illuminate the segments of the digit whose corresponding anode signal is asserted.

To illuminate a segment, the anode should be driven high while the cathode is driven low. However, since the Basys-3 uses transistors to drive enough current into the common anode point, the anode enables are inverted. Therefore, both the AN0..3 and the CA..G/DP signals are driven low when active.

Fig 18. Common anode circuit node.

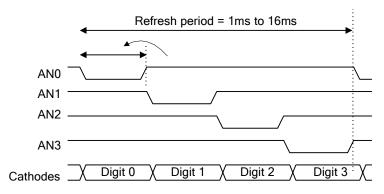

A scanning display controller circuit can be used to show a four-digit number on this display. This circuit drives the anode signals and corresponding cathode patterns of each digit in a repeating, continuous succession at an updaterate that is faster than the human eye can detect. Each digit is

illuminated just one-fourth of the time, but because the eye cannot perceive the darkening of a digit before it is illuminated again, the digit appears continuously illuminated. If the update, or "refresh", rate is slowed to around 45Hz, a flicker can be noticed in the display.